The University of New Hampshire InterOperability Laboratory iol.unh

82 Slides2.68 MB

The University of New Hampshire InterOperability Laboratory www.iol.unh.edu Serial ATA (SATA) Protocol Chapter 10 – Transport Layer

Outline Transport Layer Overview Frame Information Structure (FIS) FIS Types Host Transport States Device Transport States

Transport Layer Overview The Transport layer does not need to be aware of how frames are transmitted and received The transport layer simply constructs Frame Information Structures (FISes) for transmission and decomposes received Frame Information Structures.

Transport Layer Overview Host and device Transport layer state differ in that the source of the FIS content differs. The transport layer maintains no context in terms of ATA commands or previous FIS content.

FIS Construction When requested to construct a FIS by a higher layer, the Transport layer provides the following services: - Gathers FIS content based on the type of FIS requested Places FIS content in the proper order. Notifies the Link layer or required frame transmission and passes FIS content to Link. Manages Buffer/FIFO flow, notifies Link of required flow control. Receives frame receipt acknowledge from Link Layer. Reports good transmission of errors to requesting higher layer.

FIS Decomposition When a FIS is received from the Link layer, the Transport layer provides the following services: - Receives the FIS from the Link layer. Determines FIS type. Distributes the FIS content to the locations indicated by the FIS type. For the host Transport layer, receipt of a FIS may also cause the construction of a FIS to be returned to the device. Reports good reception or errors to higher layer

Outline Transport Layer Overview Frame Information Structure (FIS) FIS Types Host Transport States Device Transport States

Frame Format A FIS is a group of Dwords that convey information between host and device. Primitives are used to define the boundaries of the FIS and may be inserted to control the rate of the information flow.

Frame Format A primitive is a defined sequence of 4 bytes, beginning with a special 10-bit character such as a K28.5 or K28.3. SATA and SAS primitives are used for a variety of signaling and handshaking functions, and perform most of the lowlevel, time-critical functions.

Frame Format The SATA frame begins with a Start-ofFrame (SOF). The SOF is followed by the Frame Information Structure (FIS). The Cyclic Redundancy Code (CRC) is then placed in the frame. The final block in the message is an End-of-Frame (EOF).

Frame Format SOF and EOF are primitives to begin and end each frame.

Outline Transport Layer Overview Frame Information Structure (FIS) FIS Types Host Transport States Device Transport States

FIS Types The value for the FIS Type fields of all FISes has been selected to provide additional robustness. In minimally buffered implementations that may not buffer a complete FIS, the state machines may begin acting on the received FIS Type value prior to the ending CRC having been checked.

FIS Type Values The following is a table that specifies the FIS Type values and their assignments.

FIS Type Value Assignments

Register FIS - Host to Device (27h) The Register - Host to Device FIS is used to transfer the contents of the Shadow Register Block from the host to the device. The Shadow Register Block is used to generate control values which are necessary for the transfer of data to and from the non-volatile semiconductor memory device. This is the mechanism for issuing ATA commands to the device.

Register FIS - Device to Host (34h) The Register - Device to Host FIS is used by the device to update the contents of the host adapter’s Shadow Register Block. This mechanism by which devices indicate command completion status or otherwise change the contents of the host adapter’s Shadow Register Block. Transmission of a Register - Device to Host FIS is initiated by the device in order to update the contents of the host adapter’s Shadow Register Block. Transmission of this FIS is typically a result of command completion by the device.

DMA Activate FIS– Device to Host (39h) The DMA Activate FIS is used by the device to signal the host to proceed with a DMA data transfer of data from the host to the device. The device transmits a DMA Activate to the host in order to initiate the flow of DMA data from the host to the device as part of the data transfer portion of a corresponding DMA write command.

DMA Setup FIS – Bi-directional (41h) The DMA Setup FIS is the mechanism by which first-party DMA access to host memory is initiated. This FIS is used to request the host or device to program its DMA controller before transferring data.

DATA FIS – Bi-directional (46h) The Data – Bi-directional FIS is used for transporting payload data, such as the data read from or written to a number of sectors on a hard drive. The FIS may either be generated by the device to transmit data to the host or may be generated by the host to transmit data to the device.

BIST Activate FIS – Bi-directional (58h) The BIST Activate FIS shall be used to place the receiver in one of several loopback modes. The initiator transmits a BIST Activate to the recipient in order to initiate the BIST mode of operation.

PIO Setup FIS – Device to Host (5Fh) The PIO Setup – Device to Host FIS is used by the device to provide the host adapter with sufficient information regarding a PIO data phase to allow the host adapter to efficiently handle PIO data transfers. For PIO data transfers, the device shall send to the host a PIO Setup – Device to Host FIS just before each and every data transfer FIS that is required to complete the data transfer.

Set Device Bits FIS – Device to Host (A1h) The Set Device Bits FIS is used by the device to load Shadow Register Block bits for which the device has exclusive write access. The device transmits a Set Device Bits FIS to alter one or more bits in the Error register or in the Status register in the Shadow Register Block. This FIS should be used by the device to set the SERV bit in the Status register to request service for a bus released command. When used for this purpose the device shall set the Interrupt bit to one.

Outline Transport Layer Overview Frame Information Structure (FIS) FIS Types Host Transport States Device Transport States

Host Transport States FIS reception is asynchronous in nature. In the case of a non-Data FIS transmission, the host may be pre-empted by a non-Data FIS reception from the device. The host shall hold off on the pending transmission and process the incoming FIS from the device before attempting to retransmit the pending FIS.

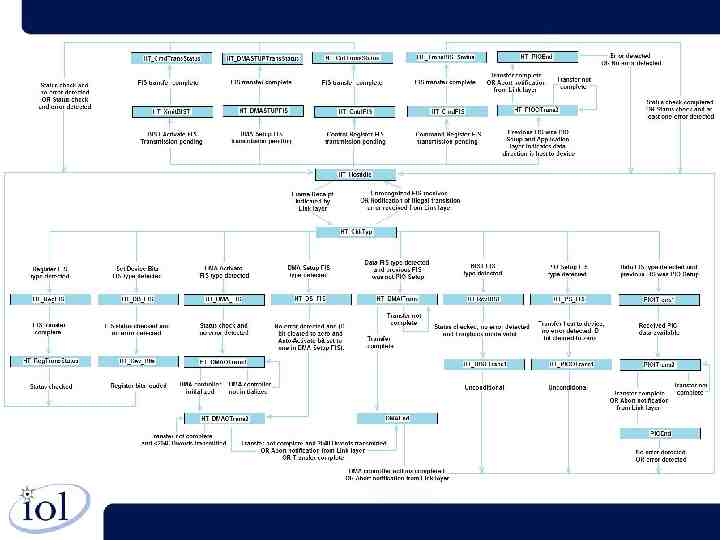

Host Transport Idle State Diagram The following slide depicts the host transport idle states in the form of a flow chart:

HT HostIdle This state is entered when a FIS transaction has been completed by the Transport layer. When in this state, the Transport layer waits for the shadow Command register to be written, the shadow Device Control register to be written, or the Link layer to indicate that a FIS is being received.

HT ChkTyp This state is entered when the Link layer indicates that a FIS is being received. When in this state, the Transport layer checks the FIS type of the incoming FIS.

HT CmdFIS This state is entered when the shadow Command register is written. When in this state, the Transport layer constructs a Register – Host to Device FIS with C bit set to one, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

HT CmdTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy layer ending status for the FIS and take appropriate error handling action if required.

HT CntrlFIS This state is entered when the shadow Device Control register is written. When in this state, the Transport layer constructs a Register – Host to Device FIS with C bit cleared to zero, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

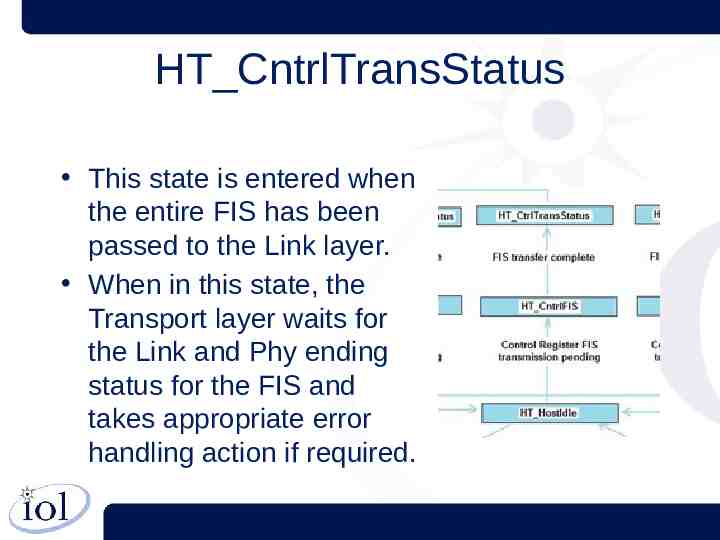

HT CntrlTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy ending status for the FIS and takes appropriate error handling action if required.

HT DMASTUPFIS This state is entered when the Application requests the transmission of a DMA Setup – Host to Device or Device to Host FIS. When in this state, the Transport layer constructs a DMA Setup – Host to Device or Device to Host FIS, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

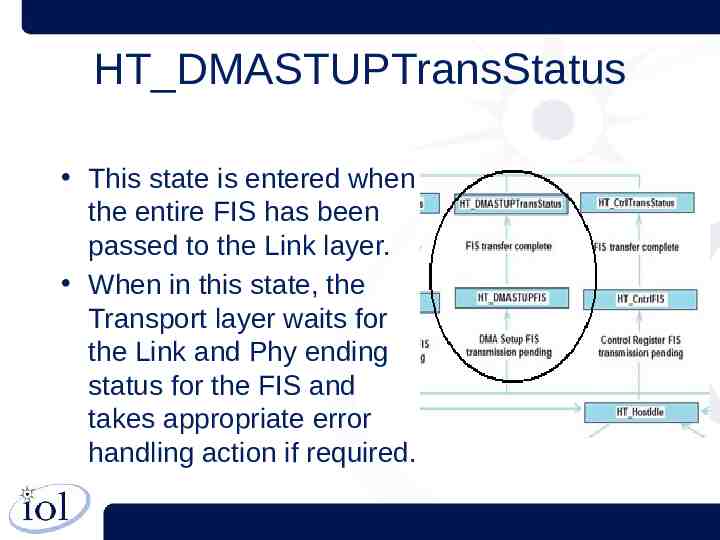

HT DMASTUPTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy ending status for the FIS and takes appropriate error handling action if required.

HT XmitBIST This state is entered to send a BIST FIS to the device.

HT TransBISTStatus This state is entered when the entire FIS has been passed to the Link layer.

HT RegFIS This state is entered when the Link layer has indicated that a FIS is being received and that the FIS is of the register type. When in this state, the Transport layer decomposes the Register FIS and places the contents into the appropriate holding registers.

HT RegTransStatus This state is entered when the entire FIS has been placed into the holding registers. When in this state, the Transport layer waits for the Link and Phy layer ending status for the FIS and takes appropriate error handling action if required.

HT DB FIS This state is entered when the Link layer has indicated that a FIS is being received and that the FIS is a Set Device Bits type. When in this state, the Transport layer waits for the FIS reception to complete and for Link and Phy layer ending status to be posted.

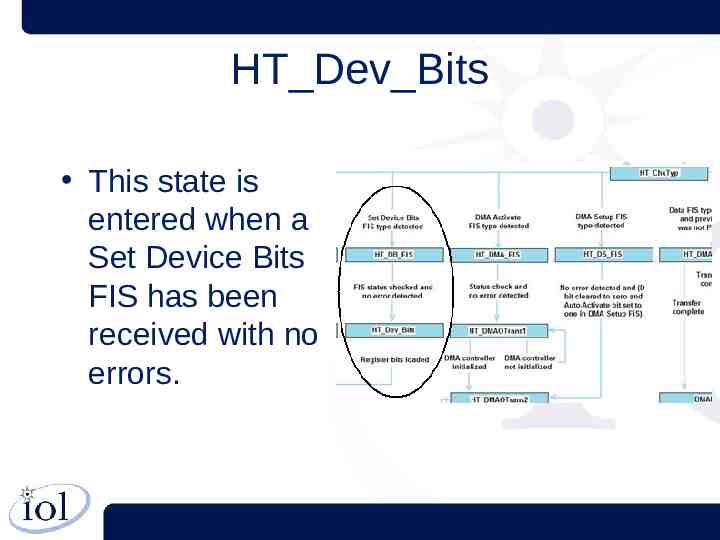

HT Dev Bits This state is entered when a Set Device Bits FIS has been received with no errors.

HT DS FIS This state is entered when the Link layer has indicated that a FIS is being received and that the Transport layer has determined the FIS is of the DMA Setup type. When in this state, the Transport layer shall initialize the DMA controller with content from the FIS.

HT DMA FIS This state is entered when the Link layer has indicated that a FIS is being received and the Transport layer has determined that a DMA Activate FIS is being received. When in this state, the Transport layer determines the direction of the DMA transfer being activated.

HT DMAOTrans1 This state is entered when it is determined that the DMA transfer that is being activated is a transfer from host to device. When in this state, the Transport layer determines if the DMA controller has been initialized.

HT DMAOTrans2 This state is entered when the DMA controller has been initialized. When in this state, the Transport layer shall activate the DMA controller and pass data to the Link layer.

HT DMAITrans This state is entered when the Transport layer has determined that the DMA transfer being activated is from device to host. When in this state, the Transport layer activates the DMA controller if the DMA controller is initialized. A data frame is received from the device and a received data Dword shall be placed in the data FIFO Also in this state, the Transport layer waits until the Link layer has begun to receive the DMA data frame and data is available to be read by the host.

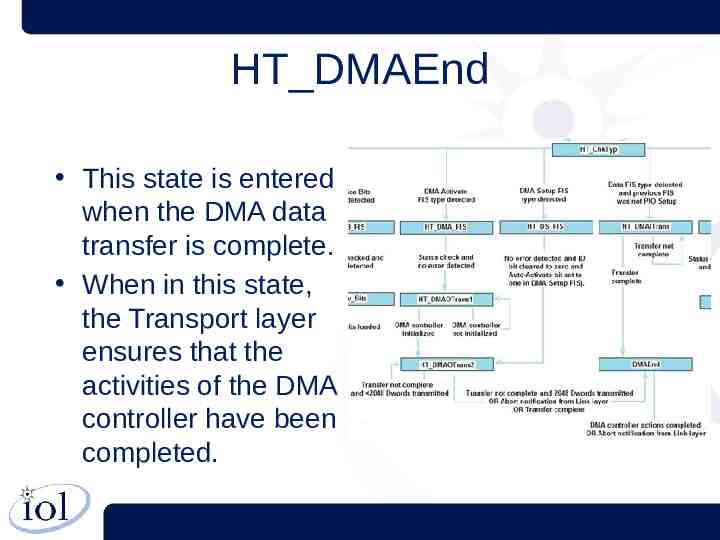

HT DMAEnd This state is entered when the DMA data transfer is complete. When in this state, the Transport layer ensures that the activities of the DMA controller have been completed.

HT PS FIS This state is entered when the Link layer has indicated that a FIS is being received and that the Transport layer has determined a PIO Setup FIS is being received. When in this state, the Transport layer determines the direction of the requested PIO transfer and indicates that the last FIS sent was a PIO Setup.

HT PIOOTrans1 This state is entered when the direction of the requested PIO data transfer is from host to device. When in this state, the Transport layer places the FIS initial register content into the shadow registers, the FIS byte count, and sets the interrupt pending flag if the FIS indicates to do so.

HT PIOOTrans2 This state is entered when PIO data is available in the PIO FIFO to be passed to the Link layer. When in this state, the Transport layer waits for the Link layer to indicate that all data has been transferred.

HT PIOEnd This state is entered when the PIO data transfer is complete. When in this state, the Transport layer places the ending register content from the received PIO request FIS into the shadow registers.

HT PIOITrans1 This state is entered when the direction of the PIO data transfer is device to host. When in this state, the Transport layer waits until the Link layer has begun to receive the PIO data frame and when data is available to be read by the host.

HT PIOITrans2 This state is entered when PIO data is available in the PIO FIFO to be read by the host and the initial shadow register content has been set. When in this state, the Transport layer waits for the Link layer to indicate that the data transfer is complete.

HT RcvBIST This state is entered when the Link layer has indicated that a FIS is being received and the Transport layer has determined that a BIST Activate FIS is being received. When in this state, the Transport layer determines the validity of the loopback request.

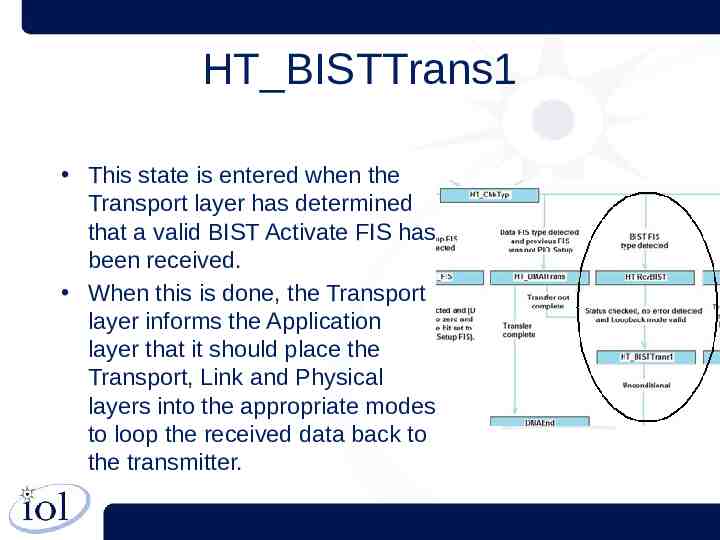

HT BISTTrans1 This state is entered when the Transport layer has determined that a valid BIST Activate FIS has been received. When this is done, the Transport layer informs the Application layer that it should place the Transport, Link and Physical layers into the appropriate modes to loop the received data back to the transmitter.

Outline Transport Layer Overview Frame Information Structure (FIS) FIS Types Host Transport States Device Transport States

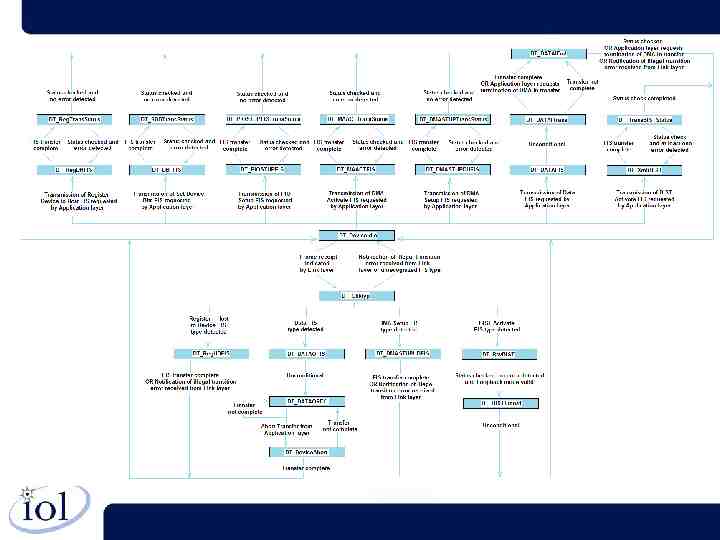

Device Transport States The following slide depicts the device transport idle states in the form of a flow chart:

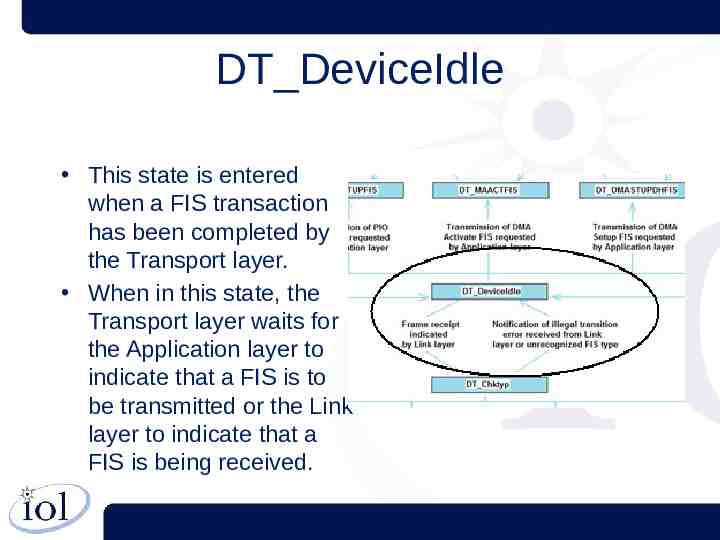

DT DeviceIdle This state is entered when a FIS transaction has been completed by the Transport layer. When in this state, the Transport layer waits for the Application layer to indicate that a FIS is to be transmitted or the Link layer to indicate that a FIS is being received.

DT ChkTyp This state is entered when the Transport layer is idle and Link layer indicates that a FIS is being received. When in this state, the Transport layer checks the FIS type of the incoming FIS.

DT RegDHFIS This state is entered when the Application requests the transmission of a Register – Device to Host FIS. When in this state, the Transport layer constructs a Register – Device to Host FIS, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

DT RegTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy layer ending status for the FIS and takes appropriate error handling action if required.

DT DB FIS This state is entered when the Application layer requests the transmission of a Set Device Bits FIS. When in this state, the Transport layer constructs a Set Device Bits FIS, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

SDBTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy layer ending status for the FIS and takes appropriate error handling action if required.

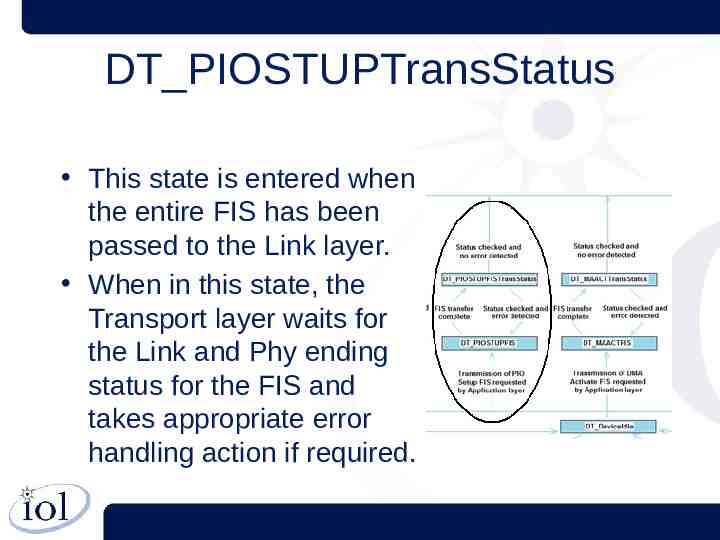

DT PIOSTUPFIS This state is entered when the Application layer requests the transmission of a PIO Setup – Device to Host FIS. When in this state, the Transport layer constructs a PIO Setup – Device to Host FIS, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

DT PIOSTUPTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy ending status for the FIS and takes appropriate error handling action if required.

DT DMAACTFIS This state is entered when the Application layer requests the transmission of a DMA Activate FIS. When in this state, the Transport layer constructs a DMA Activate FIS, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

DT DMAACTTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy ending status for the FIS and takes appropriate error handling action if required.

DT DMASTUPDHFIS This state is entered when the Application layer requests the transmission of a DMA Setup – Device to Host FIS. When in this state, the Transport layer constructs a DMA Setup – Device to Host FIS, notifies the Link layer that the FIS is to be transmitted, and passes the FIS to the Link layer.

DT DMASTUPTransStatus This state is entered when the entire FIS has been passed to the Link layer. When in this state, the Transport layer waits for the Link and Phy ending status for the FIS and takes appropriate error handling action if required.

DT DATAIFIS This state is entered when the Application layer has requested the transmission of a Data – Device to Host FIS. When in this state the Transport layer passes a portion of the DMA data to the Link layer.

DT DATAITrans This state is entered when data is available in the FIFO to be passed to the Link layer. When in this state, the Transport layer passes a Dword of data from the FIFO to the Link layer.

DT DATAIEnd This state is entered when the data transfer is complete or an abort has been requested by the Application layer. When in this state, the Transport layer waits for the Link layer and Phy layer ending status for the FIS and takes appropriate error handling action if required.

DT XmitBIST This state is entered to send a BIST FIS to the host.

DT TransBISTStatus This state is entered when the entire FIS has been passed to the Link layer.

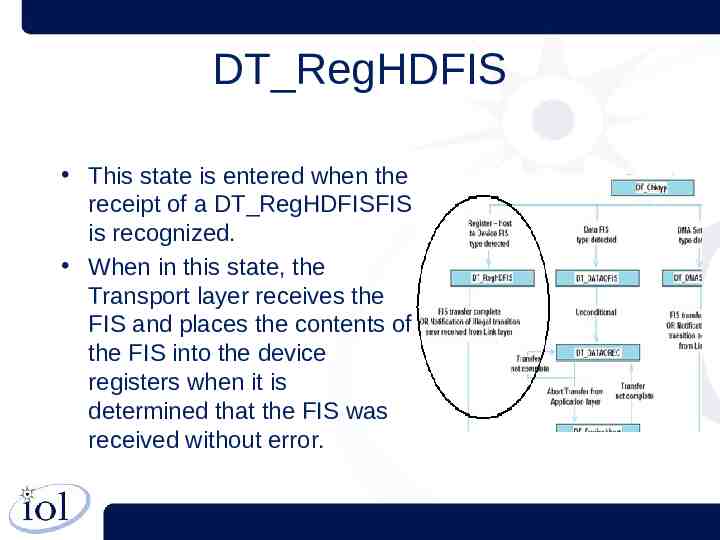

DT RegHDFIS This state is entered when the receipt of a DT RegHDFISFIS is recognized. When in this state, the Transport layer receives the FIS and places the contents of the FIS into the device registers when it is determined that the FIS was received without error.

DT DATAOFIS This state is entered when the Link layer has indicated that a FIS is being received and that the Transport layer has determined the FIS is of Data - Host to Device type. When in this state, the Transport layer prepares to receive the data.

DT DATAOREC This state is entered when the Transport layer is ready to receive the data. When in this state, the Transport layer waits for the Link layer to indicate the transfer is complete.

DT DeviceAbort This state is entered when the Application layer indicates that the current transfer is to be aborted. When in this state, the Transport layer signals the Link layer to Abort the incoming transmission and return to either DT DATAOREC or DT DeviceIdle, depending upon the current state of the FIFO.

DT DMASTUPHDFIS This state is entered when the receipt of a DT DMASTUP FIS is recognized.

DT RcvBIST This state is entered when the Link layer has indicated that a FIS is being received and the Transport layer has determined that a BIST Activate FIS is being received. When in this state, the Transport layer determines the validity of the loopback request.

DT BISTTrans1 This state is entered when the Transport layer has determined that a valid BIST Activate FIS has been received. When this happens, the Transport layer informs the Application layer that it should place the Transport, Link and Physical layers into the appropriate modes to loop the received data back to the transmitter.