CSE 675.02: Introduction to Computer Architecture Performances

52 Slides583.50 KB

CSE 675.02: Introduction to Computer Architecture Performances of Computer Systems Presentation C Gojko Babić 06/27/2005 Presentation C

Performance Measure, Report, and Summarize Make intelligent choices See through the marketing hype Key to understanding underlying organizational motivation Why is some hardware better than others for different programs? What factors of system performance are hardware related? (e.g., Do we need a new machine, or a new operating system?) How does the machine's instruction set affect performance? g. babic Presentation C

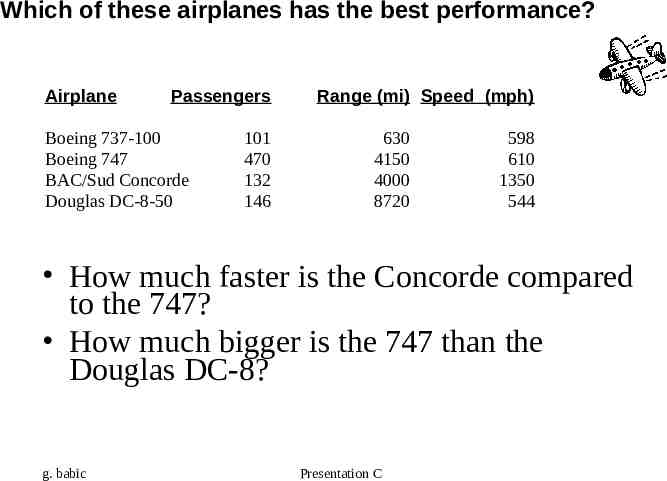

Which of these airplanes has the best performance? Airplane Passengers Boeing 737-100 Boeing 747 BAC/Sud Concorde Douglas DC-8-50 101 470 132 146 Range (mi) Speed (mph) 630 4150 4000 8720 598 610 1350 544 How much faster is the Concorde compared to the 747? How much bigger is the 747 than the Douglas DC-8? g. babic Presentation C

Basic Performance Metrics Response time: the time between the start and the completion of a task (in time units) Throughput: the total amount of tasks done in a given time period (in number of tasks per unit of time) Example: Car assembly factory: – 4 hours to produce a car (response time), – 6 cars per an hour produced (throughput) In general, there is no relationship between those two metrics, – throughput of the car assembly factory may increase to 18 cars per an hour without changing time to produce one car. – How? g. babic Presentation C 4

Computer Performance: Introduction The computer user is interested in response time (or execution time) – the time between the start and completion of a given task (program). The manager of a data processing center is interested in throughput – the total amount of work done in given time. The computer user wants response time to decrease, while the manager wants throughput increased. Main factors influencing performance of computer system are: – processor and memory, – input/output controllers and peripherals, – compilers, and – operating system. g. babic Presentation C 5

Computer Performance: TIME, TIME, TIME Response Time (latency) — How long does it take for my job to run? — How long does it take to execute a job? — How long must I wait for the database query? Throughput — How many jobs can the machine run at once? — What is the average execution rate? — How much work is getting done? If we upgrade a machine with a new processor what do we increase? If we add a new machine to the lab what do we increase? g. babic Presentation C

Execution Time Elapsed Time – counts everything (disk and memory accesses, I/O , etc.) – a useful number, but often not good for comparison purposes CPU time – doesn't count I/O or time spent running other programs – can be broken up into system time, and user time Our focus: user CPU time – time spent executing the lines of code that are "in" our program g. babic Presentation C

Analysis of CPU Time CPU time depends on the program which is executed, including: – a number of instructions executed, – types of instructions executed and their frequency of usage. Computers are constructed is such way that events in hardware are synchronized using a clock. Clock rate is given in Hz ( 1/sec). A clock rate defines durations of discrete time intervals called clock cycle times or clock cycle periods: g. babic Presentation C 8

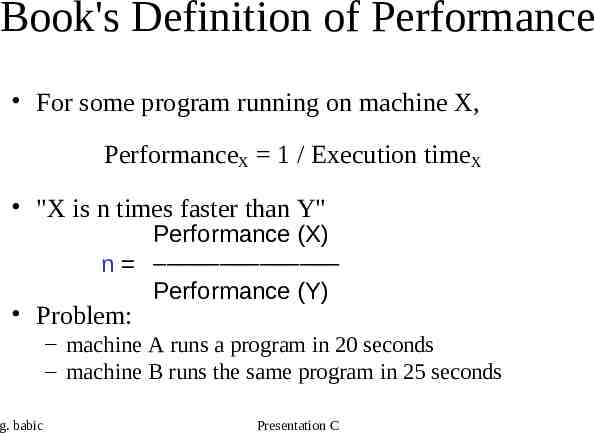

Book's Definition of Performance For some program running on machine X, PerformanceX 1 / Execution timeX "X is n times faster than Y" Performance (X) n –––––––––––––– Performance (Y) Problem: – machine A runs a program in 20 seconds – machine B runs the same program in 25 seconds g. babic Presentation C

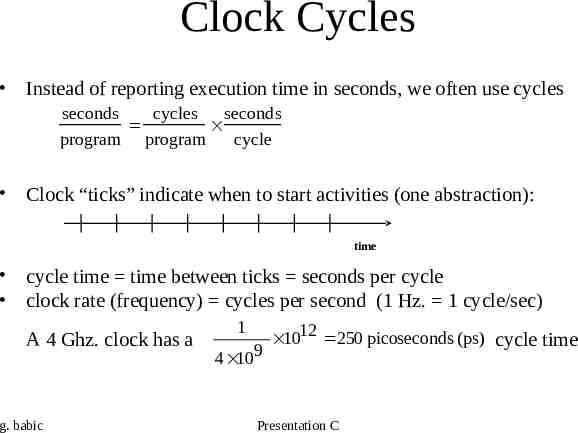

Clock Cycles Instead of reporting execution time in seconds, we often use cycles seconds cycles seconds program program cycle Clock “ticks” indicate when to start activities (one abstraction): time cycle time time between ticks seconds per cycle clock rate (frequency) cycles per second (1 Hz. 1 cycle/sec) A 4 Ghz. clock has a g. babic 1 4 109 1012 250 picoseconds (ps) cycle time Presentation C

How to Improve Performance seconds cycles seconds program program cycle So, to improve performance (everything else being equal) you can either (increase or decrease?) the # of required cycles for a program, or the clock cycle time or, said another way, the clock rate. g. babic Presentation C

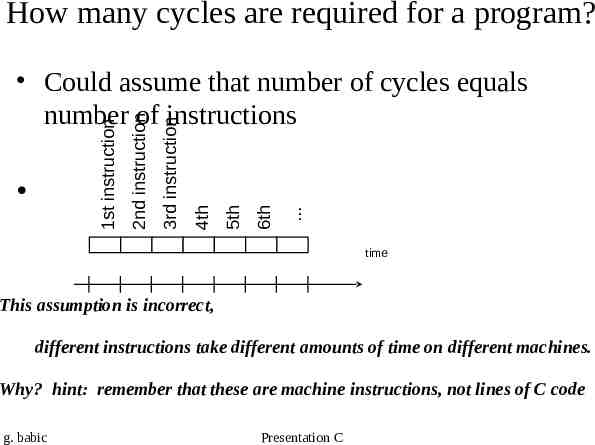

How many cycles are required for a program? . 6th 5th 4th 3rd instruction 2nd instruction 1st instruction Could assume that number of cycles equals number of instructions time This assumption is incorrect, different instructions take different amounts of time on different machines. Why? hint: remember that these are machine instructions, not lines of C code g. babic Presentation C

Different numbers of cycles for different instructions time Multiplication takes more time than addition Floating point operations take longer than integer ones Accessing memory takes more time than accessing registers Important point: changing the cycle time often changes the number of cycles required for various instructions (more later) g. babic Presentation C

Example Our favorite program runs in 10 seconds on computer A, which has a 4 GHz. clock. We are trying to help a computer designer build a new machine B, that will run this program in 6 seconds. The designer can use new (or perhaps more expensive) technology to substantially increase the clock rate, but has informed us that this increase will affect the rest of the CPU design, causing machine B to require 1.2 times as many clock cycles as machine A for the same program. What clock rate should we tell the designer to target?" g. babic Presentation C

Now that we understand cycles A given program will require – some number of instructions (machine instructions) – some number of cycles – some number of seconds We have a vocabulary that relates these quantities: – cycle time (seconds per cycle) – clock rate (cycles per second) – CPI (cycles per instruction) a floating point intensive application might have a higher CPI – MIPS (millions of instructions per second) this would be higher for a program using simple instructions g. babic Presentation C

Performance Performance is determined by execution time Do any of the other variables equal performance? – – – – – # of cycles to execute program? # of instructions in program? # of cycles per second? average # of cycles per instruction? average # of instructions per second? Common pitfall: thinking one of the variables is indicative of performance when it really isn’t. g. babic Presentation C

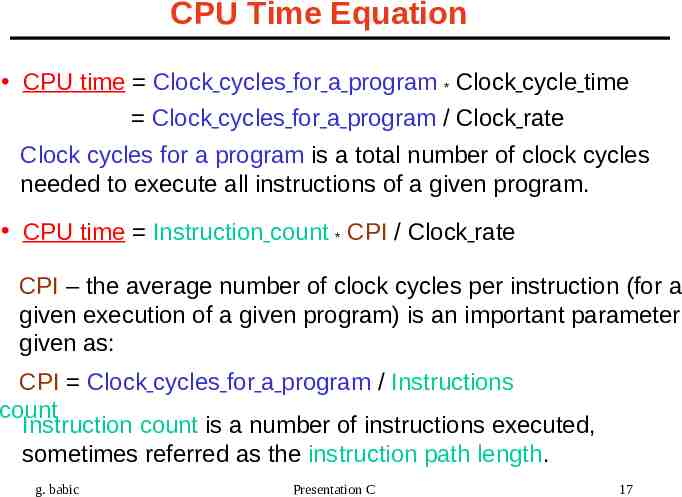

CPU Time Equation CPU time Clock cycles for a program * Clock cycle time Clock cycles for a program / Clock rate Clock cycles for a program is a total number of clock cycles needed to execute all instructions of a given program. CPU time Instruction count * CPI / Clock rate CPI – the average number of clock cycles per instruction (for a given execution of a given program) is an important parameter given as: CPI Clock cycles for a program / Instructions count Instruction count is a number of instructions executed, sometimes referred as the instruction path length. g. babic Presentation C 17

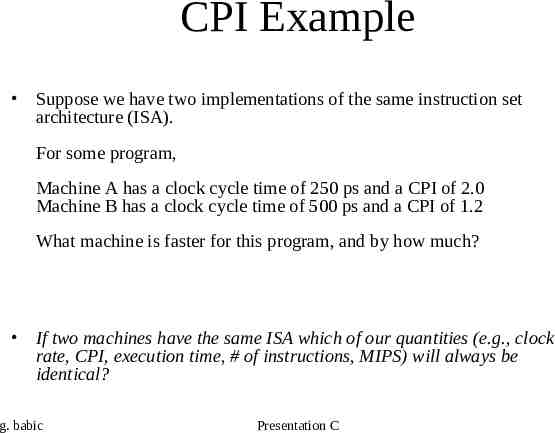

CPI Example Suppose we have two implementations of the same instruction set architecture (ISA). For some program, Machine A has a clock cycle time of 250 ps and a CPI of 2.0 Machine B has a clock cycle time of 500 ps and a CPI of 1.2 What machine is faster for this program, and by how much? If two machines have the same ISA which of our quantities (e.g., clock rate, CPI, execution time, # of instructions, MIPS) will always be identical? g. babic Presentation C

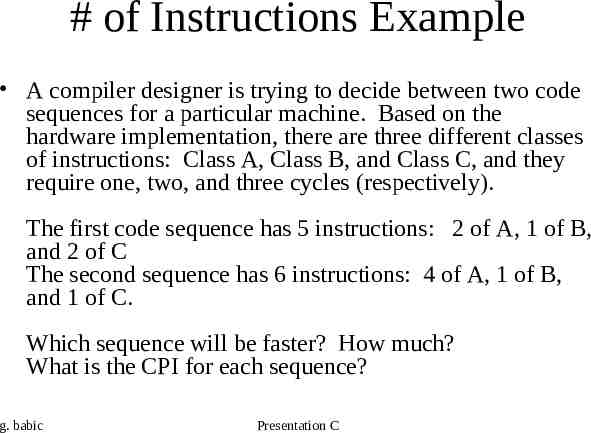

# of Instructions Example A compiler designer is trying to decide between two code sequences for a particular machine. Based on the hardware implementation, there are three different classes of instructions: Class A, Class B, and Class C, and they require one, two, and three cycles (respectively). The first code sequence has 5 instructions: 2 of A, 1 of B, and 2 of C The second sequence has 6 instructions: 4 of A, 1 of B, and 1 of C. Which sequence will be faster? How much? What is the CPI for each sequence? g. babic Presentation C

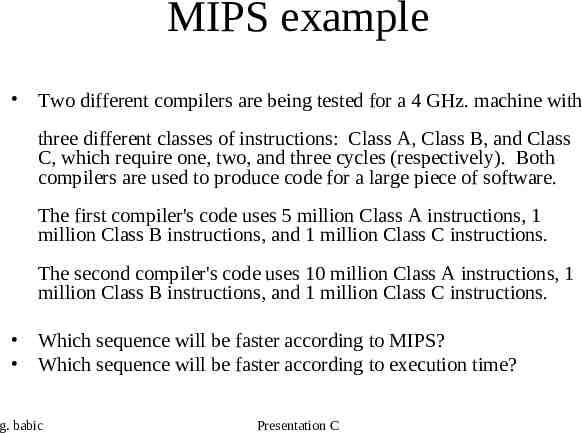

MIPS example Two different compilers are being tested for a 4 GHz. machine with three different classes of instructions: Class A, Class B, and Class C, which require one, two, and three cycles (respectively). Both compilers are used to produce code for a large piece of software. The first compiler's code uses 5 million Class A instructions, 1 million Class B instructions, and 1 million Class C instructions. The second compiler's code uses 10 million Class A instructions, 1 million Class B instructions, and 1 million Class C instructions. Which sequence will be faster according to MIPS? Which sequence will be faster according to execution time? g. babic Presentation C

Phases in Instruction Execution We can divide the execution of an instruction into the following five stages: – IF: Instruction fetch – ID: Instruction decode and register fetch – EX: Execution, effective address or branch calculation – MEM: Memory access (for lw and sw instructions only) – WB: Register write back (for ALU and lw instructions) g. babic Presentation C 21

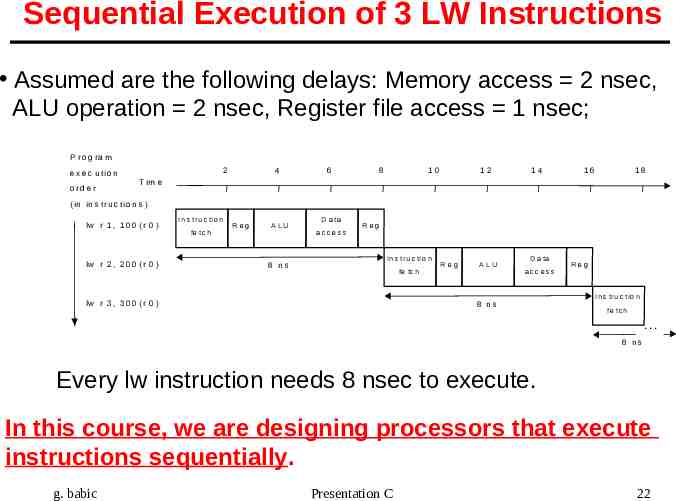

Sequential Execution of 3 LW Instructions Assumed are the following delays: Memory access 2 nsec, ALU operation 2 nsec, Register file access 1 nsec; P ro g ra m 2 e x e c u t io n o rd e r 4 6 8 10 12 14 16 18 T im e ( i n in s tr u c t io n s ) lw r 1 , 1 0 0 ( r 0 ) lw r 2 , 2 0 0 ( r 0 ) In s t ru c ti o n fe tc h R eg A LU 8 ns D a ta ac c e ss R eg In s t ru c ti o n f e tc h lw r 3 , 3 0 0 ( r 0 ) R eg A LU D a ta a ccess 8 ns R eg In s t ru c t i o n f e tc h . 8 ns Every lw instruction needs 8 nsec to execute. In this course, we are designing processors that execute instructions sequentially. g. babic Presentation C 22

CPU Time: Example 1 Consider an implementation of MIPS ISA with 500 MHz clock and – each ALU instruction takes 3 clock cycles, – each branch/jump instruction takes 2 clock cycles, – each sw instruction takes 4 clock cycles, – each lw instruction takes 5 clock cycles. Also, consider a program that during its execution executes: – x 200 million ALU instructions – y 55 million branch/jump instructions – z 25 million sw instructions – w 20 million lw instructions Find CPU time. g. babic Presentation C 23

CPU Time: Example 1 (continued) a. Approach 1: Clock cycles for a program (x 3 y 2 z 4 w 5) 910 106 clock cycles CPU time Clock cycles for a program / Clock rate 910 106 / 500 106 1.82 sec b. Approach 2: CPI Clock cycles for a program / Instructions count CPI (x 3 y 2 z 4 w 5)/ (x y z w) 3.03 clock cycles/ instruction CPU time Instruction count CPI / Clock rate (x y z w) 3.03 / 500 106 300 106 3.03 /500 106 1.82 sec g. babic Presentation C 24

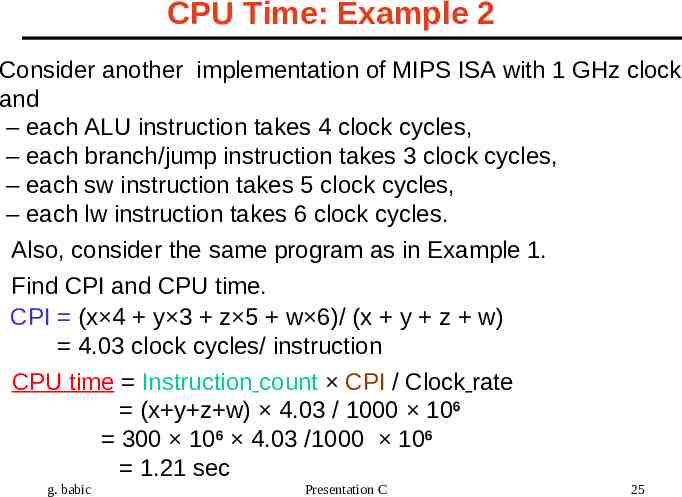

CPU Time: Example 2 Consider another implementation of MIPS ISA with 1 GHz clock and – each ALU instruction takes 4 clock cycles, – each branch/jump instruction takes 3 clock cycles, – each sw instruction takes 5 clock cycles, – each lw instruction takes 6 clock cycles. Also, consider the same program as in Example 1. Find CPI and CPU time. CPI (x 4 y 3 z 5 w 6)/ (x y z w) 4.03 clock cycles/ instruction CPU time Instruction count CPI / Clock rate (x y z w) 4.03 / 1000 106 300 106 4.03 /1000 106 1.21 sec g. babic Presentation C 25

Analysis of CPU Performance Equation CPU time Instruction count * CPI / Clock rate How to improve (i.e. decrease) CPU time: – Clock rate: hardware technology & organization, – CPI: organization, ISA and compiler technology, – Instruction count: ISA & compiler technology. Many potential performance improvement techniques primarily improve one component with small or predictable impact on the other two. g. babic Presentation C 26

Calculating Components of CPU time For an existing processor it is easy to obtain the CPU time (i.e. the execution time) by measurement, and the clock rate is known. But, it is difficult to figure out the instruction count or CPI. Newer processors, MIPS64 processor is such an example, include counters for instructions executed and for clock cycles. Those can be helpful to programmers trying to understand and tune the performance of an application. Also, different simulation techniques and queuing theory could be used to obtain values for components of the execution (CPU) time. g. babic Presentation C 27

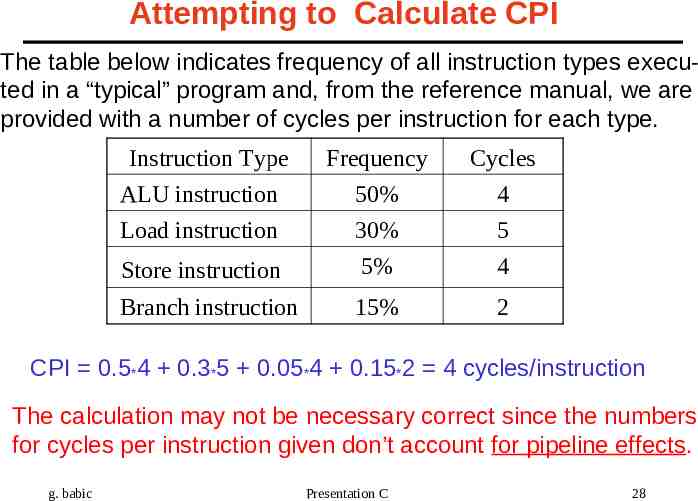

Attempting to Calculate CPI The table below indicates frequency of all instruction types executed in a “typical” program and, from the reference manual, we are provided with a number of cycles per instruction for each type. Instruction Type Frequency Cycles ALU instruction 50% 4 Load instruction 30% 5 Store instruction 5% 4 Branch instruction 15% 2 CPI 0.5*4 0.3*5 0.05*4 0.15*2 4 cycles/instruction The calculation may not be necessary correct since the numbers for cycles per instruction given don’t account for pipeline effects. g. babic Presentation C 28

Pipelining: Its Natural! Dave has four loads of clothes to wash, dry, and fold A B C D Washer takes 30 minutes Dryer takes 40 minutes “Folder” takes 20 minutes g. babic Presentation C 29

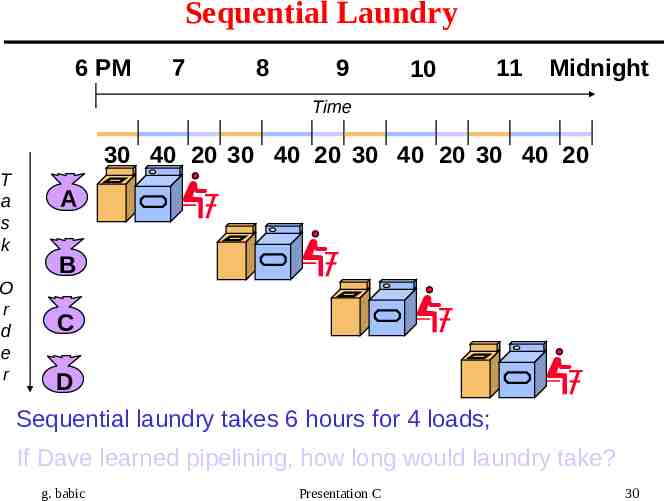

Sequential Laundry 6 PM 7 8 9 10 11 Midnight Time 30 40 20 30 40 20 30 40 20 30 40 20 T a s k O r d e r A B C D Sequential laundry takes 6 hours for 4 loads; If Dave learned pipelining, how long would laundry take? g. babic Presentation C 30

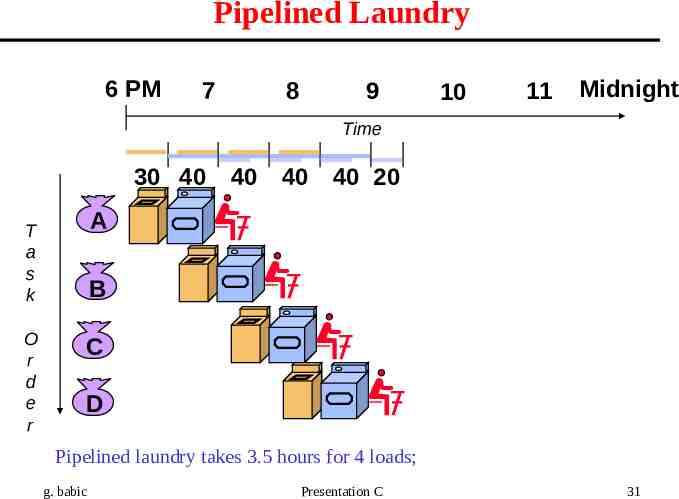

Pipelined Laundry 6 PM 7 8 9 10 11 Midnight Time 30 40 40 40 20 A T a s k O r d e r 40 B C D Pipelined laundry takes 3.5 hours for 4 loads; g. babic Presentation C 31

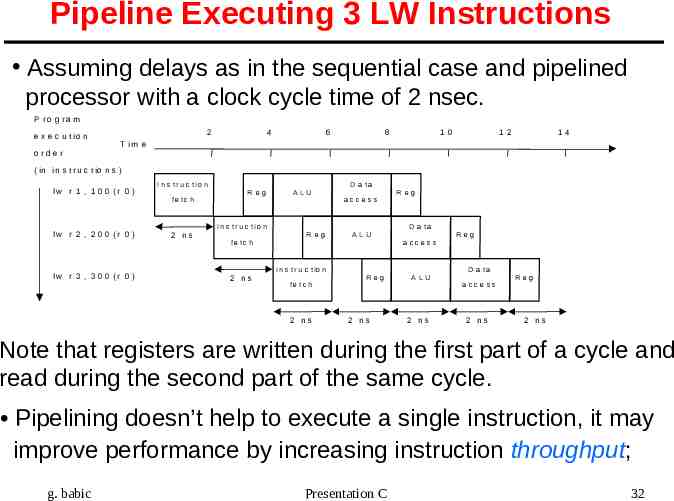

Pipeline Executing 3 LW Instructions Assuming delays as in the sequential case and pipelined processor with a clock cycle time of 2 nsec. P ro g ra m e x e c u t io n o rd e r 2 4 6 8 10 14 1 2 T im e ( in in s t r u c t io n s ) lw r 1 , 1 0 0 ( r 0 ) I n s t r u c t io n fe tc h lw r 2 , 2 0 0 ( r 0 ) lw r 3 , 3 0 0 ( r 0 ) 2 ns R eg I n s t r u c t io n fe tc h 2 ns A LU R eg I n s t r u c t io n fe tc h 2 ns D a ta access A LU R eg 2 ns R eg D a ta a cc e s s A LU 2 ns R eg D a ta a cc e s s 2 ns R eg 2 ns Note that registers are written during the first part of a cycle and read during the second part of the same cycle. Pipelining doesn’t help to execute a single instruction, it may improve performance by increasing instruction throughput; g. babic Presentation C 32

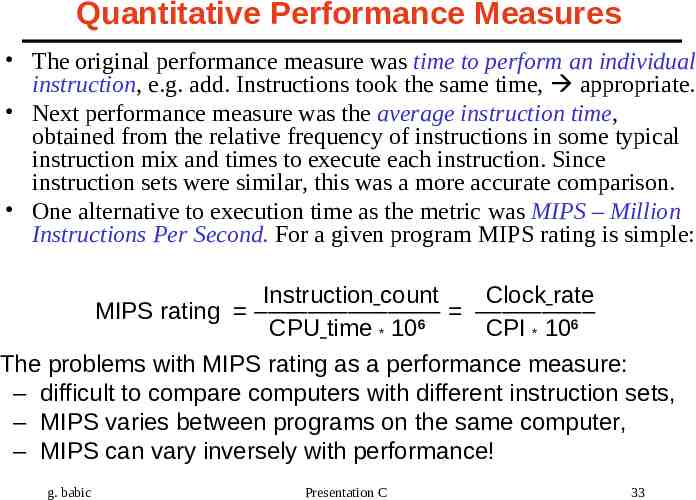

Quantitative Performance Measures The original performance measure was time to perform an individual instruction, e.g. add. Instructions took the same time, appropriate. Next performance measure was the average instruction time, obtained from the relative frequency of instructions in some typical instruction mix and times to execute each instruction. Since instruction sets were similar, this was a more accurate comparison. One alternative to execution time as the metric was MIPS – Million Instructions Per Second. For a given program MIPS rating is simple: Instruction count Clock rate MIPS rating –––––––––––––– ––––––––– 6 CPU time * 10 CPI * 106 The problems with MIPS rating as a performance measure: – difficult to compare computers with different instruction sets, – MIPS varies between programs on the same computer, – MIPS can vary inversely with performance! g. babic Presentation C 33

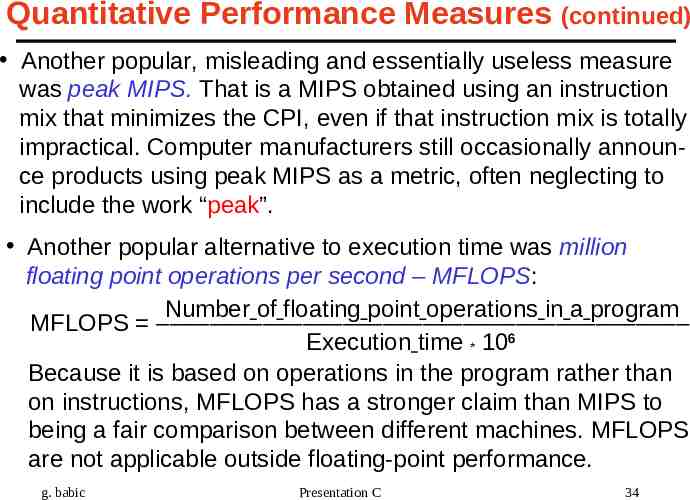

Quantitative Performance Measures (continued) Another popular, misleading and essentially useless measure was peak MIPS. That is a MIPS obtained using an instruction mix that minimizes the CPI, even if that instruction mix is totally impractical. Computer manufacturers still occasionally announce products using peak MIPS as a metric, often neglecting to include the work “peak”. Another popular alternative to execution time was million floating point operations per second – MFLOPS: Number of floating point operations in a program MFLOPS –––––––––––––––––––––––––––––––––––––––– Execution time * 106 Because it is based on operations in the program rather than on instructions, MFLOPS has a stronger claim than MIPS to being a fair comparison between different machines. MFLOPS are not applicable outside floating-point performance. g. babic Presentation C 34

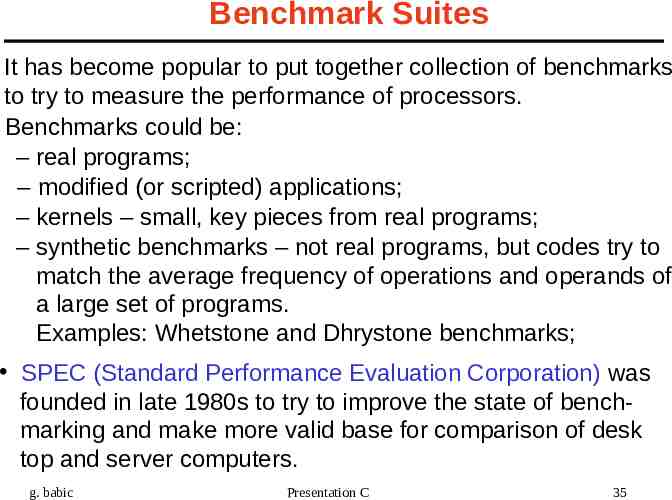

Benchmark Suites It has become popular to put together collection of benchmarks to try to measure the performance of processors. Benchmarks could be: – real programs; – modified (or scripted) applications; – kernels – small, key pieces from real programs; – synthetic benchmarks – not real programs, but codes try to match the average frequency of operations and operands of a large set of programs. Examples: Whetstone and Dhrystone benchmarks; SPEC (Standard Performance Evaluation Corporation) was founded in late 1980s to try to improve the state of benchmarking and make more valid base for comparison of desk top and server computers. g. babic Presentation C 35

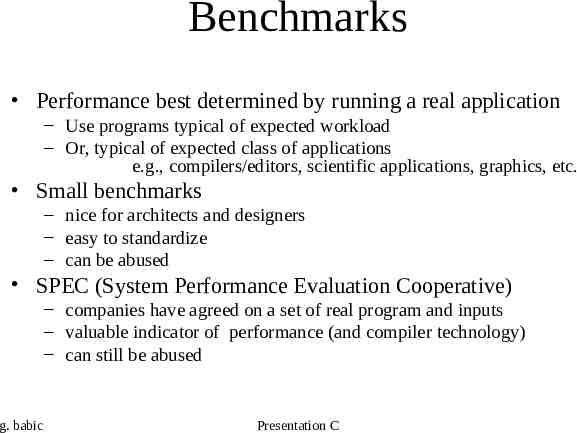

Benchmarks Performance best determined by running a real application – Use programs typical of expected workload – Or, typical of expected class of applications e.g., compilers/editors, scientific applications, graphics, etc. Small benchmarks – nice for architects and designers – easy to standardize – can be abused SPEC (System Performance Evaluation Cooperative) – companies have agreed on a set of real program and inputs – valuable indicator of performance (and compiler technology) – can still be abused g. babic Presentation C

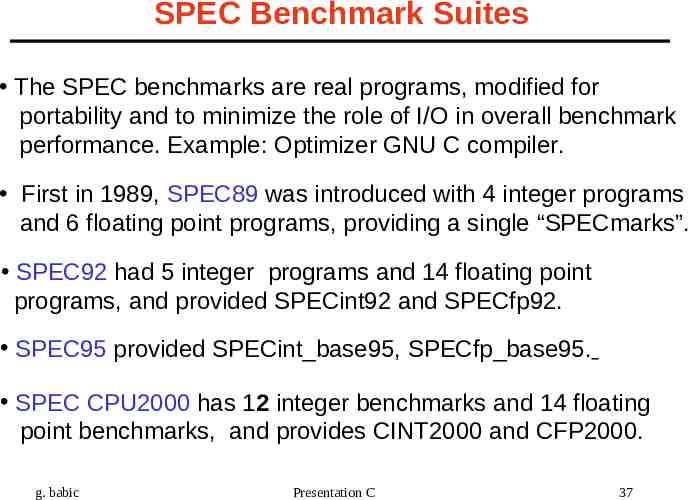

SPEC Benchmark Suites The SPEC benchmarks are real programs, modified for portability and to minimize the role of I/O in overall benchmark performance. Example: Optimizer GNU C compiler. First in 1989, SPEC89 was introduced with 4 integer programs and 6 floating point programs, providing a single “SPECmarks”. SPEC92 had 5 integer programs and 14 floating point programs, and provided SPECint92 and SPECfp92. SPEC95 provided SPECint base95, SPECfp base95. SPEC CPU2000 has 12 integer benchmarks and 14 floating point benchmarks, and provides CINT2000 and CFP2000. g. babic Presentation C 37

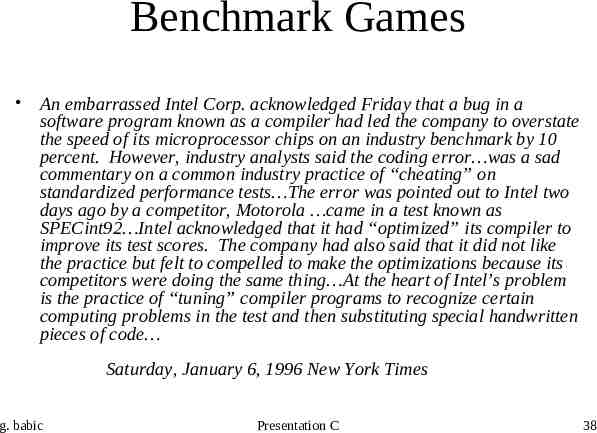

Benchmark Games An embarrassed Intel Corp. acknowledged Friday that a bug in a software program known as a compiler had led the company to overstate the speed of its microprocessor chips on an industry benchmark by 10 percent. However, industry analysts said the coding error was a sad commentary on a common industry practice of “cheating” on standardized performance tests The error was pointed out to Intel two days ago by a competitor, Motorola came in a test known as SPECint92 Intel acknowledged that it had “optimized” its compiler to improve its test scores. The company had also said that it did not like the practice but felt to compelled to make the optimizations because its competitors were doing the same thing At the heart of Intel’s problem is the practice of “tuning” compiler programs to recognize certain computing problems in the test and then substituting special handwritten pieces of code Saturday, January 6, 1996 New York Times g. babic Presentation C 38

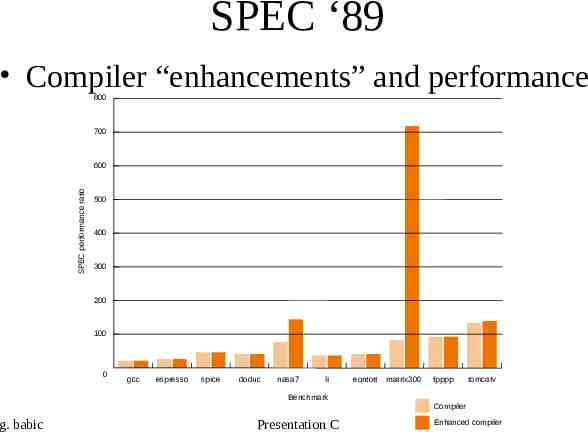

SPEC ‘89 Compiler “enhancements” and performance 800 700 SPEC performance ratio 600 500 400 300 200 100 0 gcc espresso spice doduc nasa7 li eqntott matrix300 fpppp tomcatv Benchmark Compiler g. babic Presentation C Enhanced compiler

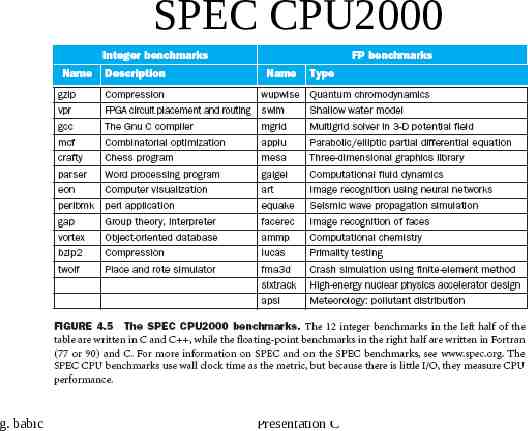

SPEC CPU2000 g. babic Presentation C

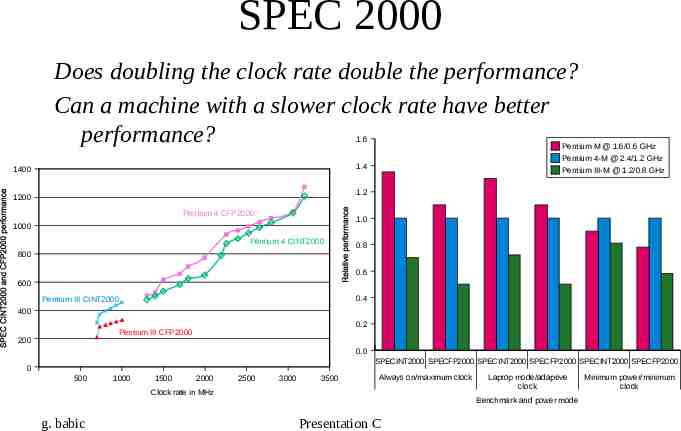

SPEC 2000 Does doubling the clock rate double the performance? Can a machine with a slower clock rate have better performance? 1.6 Pentium M @ 1.6/0.6 GHz Pentium 4-M @ 2.4/1.2 GHz Pentium III-M @ 1.2/0.8 GHz 1.4 1400 1.2 1200 Pentium 4 CFP2000 1.0 1000 Pentium 4 CINT2000 0.8 800 0.6 600 0.4 Pentium III CINT2000 400 0.2 Pentium III CFP2000 200 0.0 SPECINT2000 SPECFP2000 SPECINT2000 SPECFP2000 SPECINT2000 SPECFP2000 0 500 1000 1500 2000 2500 3000 3500 Always on/maximum clock Clock rate in MHz Laptop mode/adaptive clock Benchmark and power mode g. babic Presentation C Minimum power/minimum clock

Amdahl's Law Execution Time After Improvement Execution Time Unaffected ( Execution Time Affected / Amount of Improvement ) Example: "Suppose a program runs in 100 seconds on a machine, with multiply responsible for 80 seconds of this time. How much do we have to improve the speed of multiplication if we want the program to run 4 times faster?" How about making it 5 times faster? Principle: Make the common case fast g. babic Presentation C

Example Suppose we enhance a machine making all floating-point instructions run five times faster. If the execution time of some benchmark before the floating-point enhancement is 10 seconds, what will the speedup be if half of the 10 seconds is spent executing floating-point instructions? We are looking for a benchmark to show off the new floating-point unit described above, and want the overall benchmark to show a speedup of 3. One benchmark we are considering runs for 100 seconds with the old floating-point hardware. How much of the execution time would floating-point instructions have to account for in this program in order to yield our desired speedup on this benchmark? g. babic Presentation C

Remember Performance is specific to a particular program/s – Total execution time is a consistent summary of performance For a given architecture performance increases come from: – – – – increases in clock rate (without adverse CPI affects) improvements in processor organization that lower CPI compiler enhancements that lower CPI and/or instruction count Algorithm/Language choices that affect instruction count Pitfall: expecting improvement in one aspect of a machine’s performance to affect the total performance g. babic Presentation C

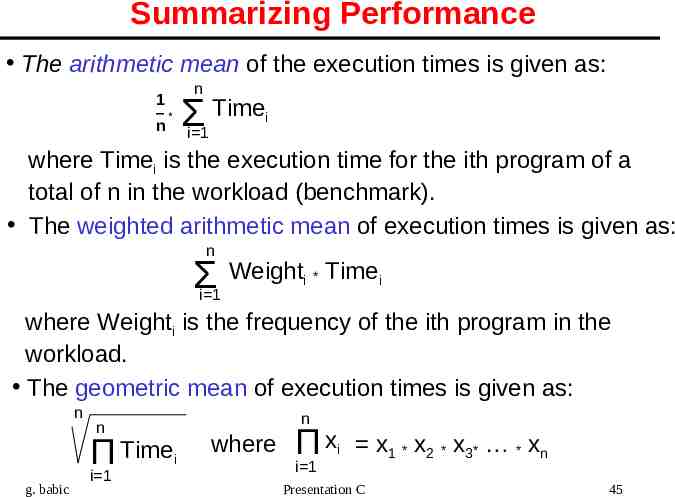

Summarizing Performance The arithmetic mean of the execution times is given as: n 1 Timei –* n i 1 Σ where Timei is the execution time for the ith program of a total of n in the workload (benchmark). The weighted arithmetic mean of execution times is given as: n Σ Weight i 1 i * Timei where Weighti is the frequency of the ith program in the workload. The geometric mean of execution times is given as: n n n Time П i 1 i g. babic where x П i 1 i x1 * x2 * x3* * xn Presentation C 45

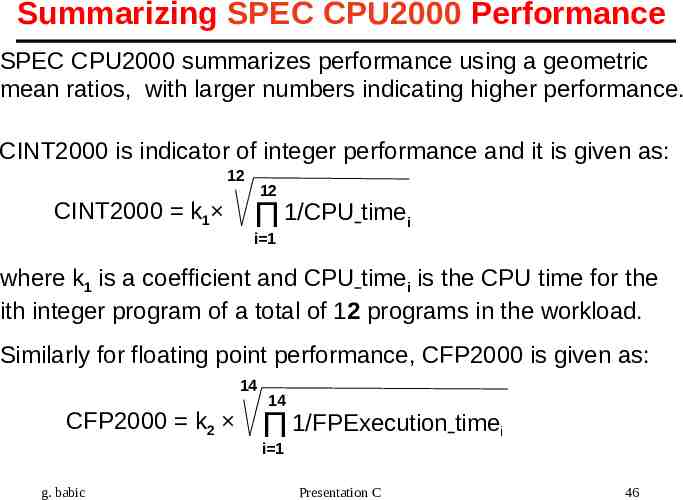

Summarizing SPEC CPU2000 Performance SPEC CPU2000 summarizes performance using a geometric mean ratios, with larger numbers indicating higher performance. CINT2000 is indicator of integer performance and it is given as: 12 CINT2000 k1 12 1/CPU time П i 1 i where k1 is a coefficient and CPU timei is the CPU time for the ith integer program of a total of 12 programs in the workload. Similarly for floating point performance, CFP2000 is given as: 14 CFP2000 k2 g. babic 14 1/FPExecution time П i 1 i Presentation C 46

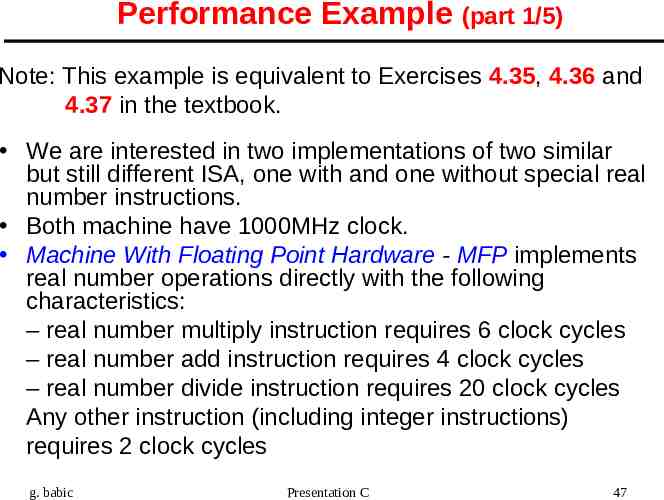

Performance Example (part 1/5) Note: This example is equivalent to Exercises 4.35, 4.36 and 4.37 in the textbook. We are interested in two implementations of two similar but still different ISA, one with and one without special real number instructions. Both machine have 1000MHz clock. Machine With Floating Point Hardware - MFP implements real number operations directly with the following characteristics: – real number multiply instruction requires 6 clock cycles – real number add instruction requires 4 clock cycles – real number divide instruction requires 20 clock cycles Any other instruction (including integer instructions) requires 2 clock cycles g. babic Presentation C 47

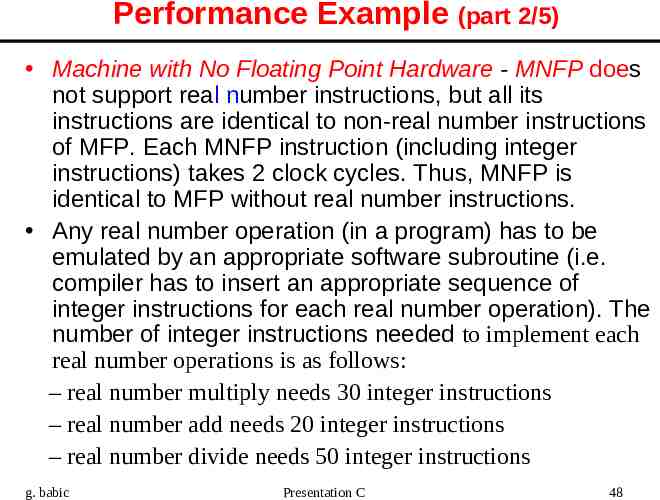

Performance Example (part 2/5) Machine with No Floating Point Hardware - MNFP does not support real number instructions, but all its instructions are identical to non-real number instructions of MFP. Each MNFP instruction (including integer instructions) takes 2 clock cycles. Thus, MNFP is identical to MFP without real number instructions. Any real number operation (in a program) has to be emulated by an appropriate software subroutine (i.e. compiler has to insert an appropriate sequence of integer instructions for each real number operation). The number of integer instructions needed to implement each real number operations is as follows: – real number multiply needs 30 integer instructions – real number add needs 20 integer instructions – real number divide needs 50 integer instructions g. babic Presentation C 48

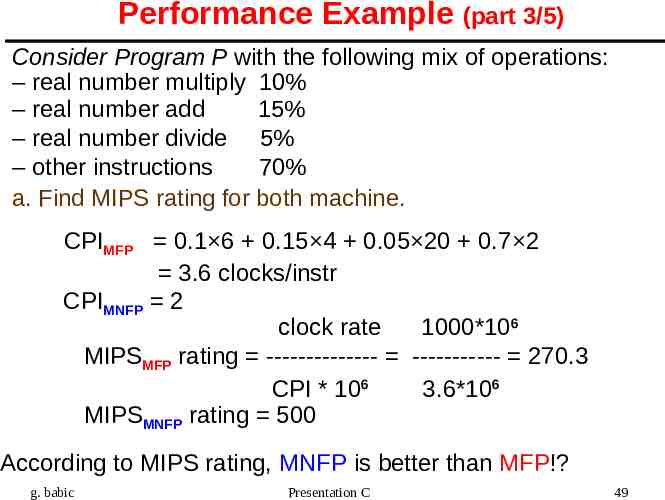

Performance Example (part 3/5) Consider Program P with the following mix of operations: – real number multiply 10% – real number add 15% – real number divide 5% – other instructions 70% a. Find MIPS rating for both machine. CPIMFP 0.1 6 0.15 4 0.05 20 0.7 2 3.6 clocks/instr CPIMNFP 2 clock rate 1000*106 MIPSMFP rating -------------- ----------- 270.3 CPI * 106 3.6*106 MIPSMNFP rating 500 According to MIPS rating, MNFP is better than MFP!? g. babic Presentation C 49

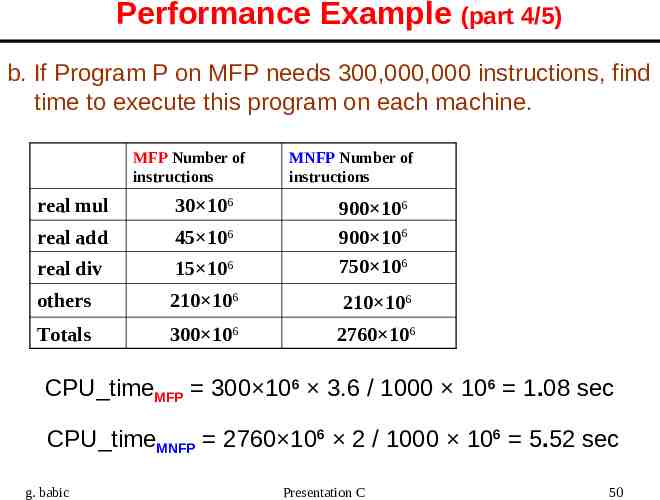

Performance Example (part 4/5) b. If Program P on MFP needs 300,000,000 instructions, find time to execute this program on each machine. MFP Number of instructions MNFP Number of instructions real mul 30 106 real add 45 106 real div 15 106 900 106 900 106 750 106 others 210 106 210 106 Totals 300 106 2760 106 CPU timeMFP 300 106 3.6 / 1000 106 1.08 sec CPU timeMNFP 2760 106 2 / 1000 106 5.52 sec g. babic Presentation C 50

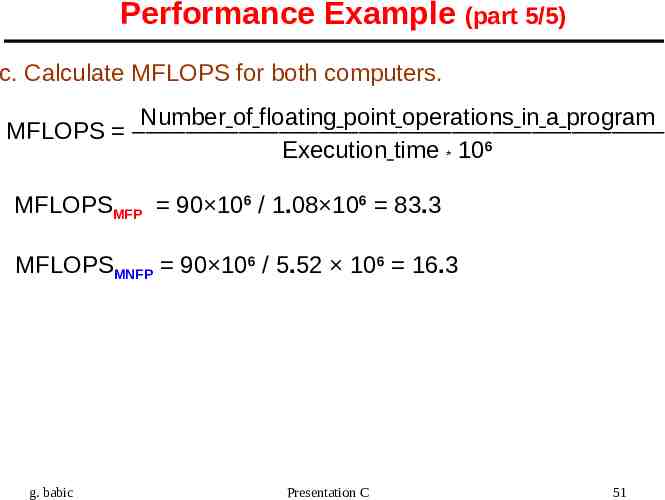

Performance Example (part 5/5) c. Calculate MFLOPS for both computers. Number of floating point operations in a program MFLOPS –––––––––––––––––––––––––––––––––––––––– Execution time * 106 MFLOPSMFP 90 106 / 1.08 106 83.3 MFLOPSMNFP 90 106 / 5.52 106 16.3 g. babic Presentation C 51

Machine With Floating Point Hardware - MFP – real number multiply instruction requires 6 clock cycles – real number add instruction requires 4 clock cycles – real number divide instruction requires 20 clock cycles Any other instruction (including integer instructions) requires 2 clock cycles Machine with No Floating Point Hardware - MNFP The number of integer instructions needed – real number multiply needs 30 integer instructions – real number add needs 20 integer instructions – real number divide needs 50 integer instructions Consider Program P with the following mix of operations: – real number multiply 10% – real number add 15% – real number divide 5% g. babic Presentation C – other instructions 70%